# Tailoring Interfacial Oxide for Polysilicon Bit-Cell Contacts and Emitters with In Situ Vapor HF Interface Cleaning and Polysilicon Deposition in a 4Mbit BiCMOS Fast Static RAM

Fred Walczyk, Craig Lage, Vidya Kaushik<sup>†</sup> and Mike Blackwell

Advanced Products Research and Development Laboratory, <sup>†</sup>MOS Analytical Laboratory Motorola Semiconductor Products Sector Austin, Texas 78762

Austin, Texas 78702

**Abstract** -- A cluster tool based technique for in situ vapor HF cleaning, ultra thin oxide growth and polysilicon deposition is compared to conventional processing in forming polysilicon emitters and polysilicon bit-cell contacts in a 4Mbit/0.5um BiCMOS FSRAM process. Results are reported which indicate that the control achieved with cluster tool processing provides greater flexibility in simultaneously optimizing the performance of both the polysilicon emitters and bit-cell contacts.

### I. INTRODUCTION

As the need for fast and high density static RAMs increases to support advanced microprocessors, the designers of fast static RAMs (FSRAMs) are frequently embracing BiCMOS methodologies to meet the access time requirements for memories at the 4Mbit level and beyond. For this application many familiar aspects of polysilicon bipolar device fabrication must be rationalized in terms of the total device fabrication process when defining a BiCMOS technology.

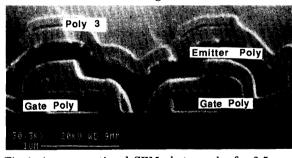

While high performance bipolar devices provide techniques for achieving fast access times in BiCMOS FSRAMs, self-aligned polysilicon bit-cell contacts provide one of the techniques for achieving a small bitcell size at the 4Mbit density level. In one bit-cell design the Vss supply voltage is brought into the memory cell without a traditional metal contact. The Vss bus, which is routed over the cell in second level polysilicon, is connected to the area between each pair of pull-down gates through a self-aligned bit-cell contact. The contact area between second level polysilicon and N+ substrate can be as small as 0.6um x 0.2um when permanent gate sidewall spacers are used. The structure of the bit-cell contact is depicted in an SEM cross section in Fig. 1.

Fig 1. A cross-sectional SEM photograph of a 0.5um Poly 2 to substrate contact self-aligned between two pull-down gates.

The aspect ratio and small dimensions of these contacts can make removal of native oxide difficult with conventional wet etching techniques.

In this paper we describe in situ processing techniques which involve removing native oxide with vapor HF, optionally growing several monolayers of thermal interfacial oxide and depositing a polysilicon film using a load locked multi-chamber cluster tool. We have examined the the capability of this process to produce low bit-cell contact resistance while tailoring bipolar gain through the use of a thin interfacial oxide. The results achieved in satisfying these competing requirements are reported.

### II. PROCESSING

The process used to produce the circuits and test structures described in this work is described in [1]. The sequence to form the bit-cell contact and polysilicon emitter is:

- o Etch Openings in Poly 1 to Poly 2 Dielectric

- o Pre-Poly 2 Deposition Clean

- o Poly 2 Deposition

- o Poly 2 Doping (Implant)

- o Poly 2 Anneal

While it is possible to produce thinner interfacial oxides with the in situ process described above, a target of 10Å of interfacial oxide was selected for the in situ oxide examined in this work. Subsequent processing capable of producing interfacial oxide breakup includes a short 1050°C Rapid Thermal Anneal (RTA) after second polysilicon doping and a similar anneal before contact etch for doped glass planarization.

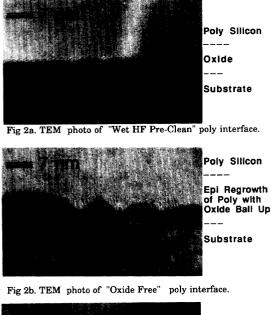

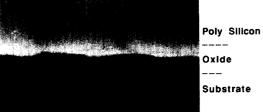

To distinguish the three processes we will compare in this work we identify the following: 1)--a traditional wet HF pre-clean and polysilicon deposition process, the "Wet HF Pre-Clean" process; 2)--an in situ vapor HF pre-clean/poly deposition process targeted to producing a minimum of interfacial oxide, the "Oxide Free" process; and 3)--an in situ vapor HF preclean/oxidation/poly deposition process targeted to produce a controlled oxide at the polysilicon interface, the "Controlled Oxide" process. In situ processing was accomplished in an ASM vertical reactor cluster tool, the Advance 600/2. Cross-section TEM imaging was used to observe and evaluate the interfaces produced by each of the three processes. The micrographs obtained are shown in Figs. 2a, b, and c. Significant observations from these TEMs are summarized in table I.

Fig 2c. TEM photo of "Controlled Oxide" poly interface.

| TABLE I                     |

|-----------------------------|

| TEM OBSERVATIONS OF EMITTER |

| INTERFACE CHARACTERISTICS   |

| Emitter Poly<br>Pre-Clean<br>Process | Oxide Epitaxial<br>Thickness Regrowth<br>in Å |                      |

|--------------------------------------|-----------------------------------------------|----------------------|

| Wet HF<br>Pre-Clean                  | 20-25 Å                                       | None                 |

| Oxide<br>Free<br>Process             | 8-10 Å                                        | Regrowth<br>Observed |

| Controlled<br>Oxide<br>Process       | 18-20 Å                                       | None                 |

A very thin and largely discontinuous interfacial oxide is seen with the "oxide free" process. In contrast, a significant oxide is present with both the "wet HF" and the "controlled oxide" process. Epitaxial regrowth of the polysilicon layer, which is suppressed by residual interfacial oxide, was observed after RTA anneal with the "oxide free" cluster tool process but not with either the "wet HF" or the "controlled oxide" process.

### III. CONTACT RESISTANCE

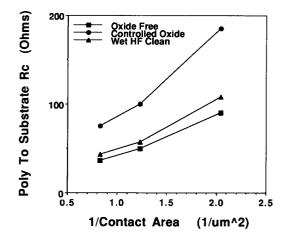

Bit-cell contact resistance (Rc), measured with Kelvin contacted structures, is plotted versus inverse contact area in Fig 3. Significantly higher contact resistance values are measured when an in situ interfacial oxide process is used than when either the "oxide free" or the conventional "wet HF" clean processes are used.

Fig 3. Bit-cell contact resistance between emitter poly and substrate is plotted against the reciprocal of contact area.

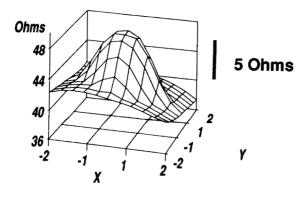

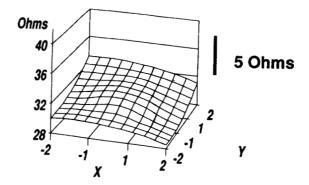

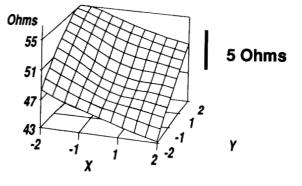

A strong radial variation in Rc is observed with the "wet HF" process while only a weak front to back dependence is seen with the "oxide free" process. A larger front to back variation in Rc is seen with the "controlled oxide" process. See Fig 4a, b, and c (last page-same vertical scale on all plots).

## IV. Polysilicon Emitter Transistor Characteristics

The emitter resistance is significantly lower and HFE roll-off is pushed out to higher emitter currents with the "oxide free" process. This is reflected in higher emitter knee current values. Emitter resistance (RE) and knee current (IKE-the emitter current for a 10% roll-off in HFE from peak HFE) are given in Table II.

| TABLE II<br>POLYSILICON EMITTER INTERFACE RELATED<br>BIPOLAR DEVICE PARAMETERS<br>BY POLYSILICON DEPOSITION PROCESS<br>FOR A 0.8umx2.4um EMITTER |           |        |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|--|--|--|

| Process                                                                                                                                          | RE        | IKE    |  |  |  |

| Oxide Free                                                                                                                                       | 18.0 ohms | 3.4 mA |  |  |  |

| Controlled                                                                                                                                       | 23.6 ohms |        |  |  |  |

2.9 mA

| Wet HF<br>Pre-Clean | 20.4 ohms | 2.5mA                                   |  |

|---------------------|-----------|-----------------------------------------|--|

|                     |           | FE roll-off across<br>ote improved high |  |

Oxide

....

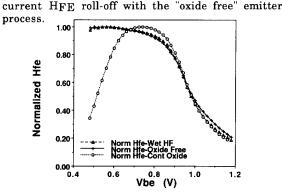

Fig 5. Normalized HFE versus VBE by polysilicon emitter deposition process. Peak HFE has been normalized to 1.0.

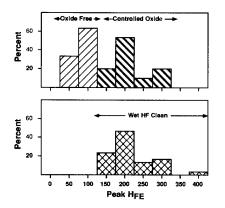

In comparing the distributions of peak HFE values for the "oxide free", the "controlled oxide" and the "wet HF" clean processes in Fig. 5., we observe the "oxide free" process produces a much lower and more tightly controlled HFE distribution than either the "controlled oxide" or the conventional "wet HF" clean process.

Fig 6. Peak HFE distributions by polysilicon emitter deposition

process. Upper left--"oxide free" in situ clean process, upper right--"controlled oxide" in situ clean and oxidation process and bottom distribution--conventional "wet HF" clean and polysilicon deposition.

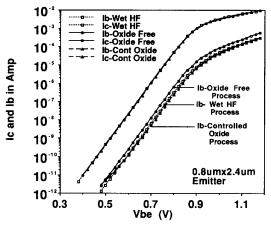

While the collector currents are very similar for all three processes, the "oxide free" process produces significantly higher base current and lower HFE; see the Gummel plots in Fig 4. below.

Fig 7. Ic and Ib versus Vbe for 0.8umx2.4um n-p-n devices by emitter poly deposition process.

Average  $H_{FE}$ , average base saturation current (IBsat) and average collector saturation current (ICsat) are summarized in table III by emitter poly deposition process. The differences in HFE among groups are directly related to the higher IBsat seen with the "oxide free" emitter process. By adjusting the thickness of the oxide barrier at the emitter interface, we are able to tailor critical bipolar device characteristics.

TABLE III PEAK HFE, BASE AND COLLECTOR SATURATION CURRENTS BY POLYSILICON DEPOSITION PROCESS

| PROCESS             |          |                               |                         |  |  |

|---------------------|----------|-------------------------------|-------------------------|--|--|

| Process             | Peak HFE | IBsat<br>(A/um <sup>2</sup> ) | $I_{Csat}$ $(A/um^2)$   |  |  |

| Oxide Free          | 79       | 0.77x 10 <sup>-20</sup>       | 0.78x 10 <sup>-18</sup> |  |  |

| Controlled<br>Oxide | 231      | 0.28x 10 <sup>-20</sup>       | 0.76x 10 <sup>-18</sup> |  |  |

| Wet HF<br>Pre-clean | 236      | 0.36x 10 <sup>-20</sup>       | 1.57x 10 <sup>-18</sup> |  |  |

### V. CONCLUSIONS

We have compared two integrated preclean/polysilicon deposition processes which provide

IEEE 1992 Bipolar Circuits and Technology Meeting 4.2

for direct control of interfacial oxide to each other and to a conventional "wet HF" clean and polysilicon deposition process. The "oxide free" process has provided reduced bit-cell contact resistance and improved HFE control while the "controlled oxide" process increases HFE. The ability to tailor interfacial oxide between poly and single crystal silicon provides the flexibility to optimize the emitter poly deposition to suit the circuit requirements of a specific BiCMOS process.

### ACKNOWLEDGMENTS

The authors would like to acknowledge the valuable technical discussions with Phil Tobin and the support of Rick Sivan in accomplishing this work. We would like to recognize the in situ processing done at the ASM development laboratory in Bilthoven, The Netherlands. We would like to thank the APRDL process and testing groups for their support, Cheryl Williams for SEM support and Gloria Estrada for TEM sample preparation.

#### REFERENCES

[1] J. Hayden et al., IEEE Trans. Electron Devices, vol. 39, pp 1669-1679, July 1992.

Fig 4a. Topological display of Rc over wafer surface for "wet HF" process.

Fig 4b. Topological display of Rc over wafer surface for "oxide free" process.

Fig 4c. Topological display of Rc over wafer surface for "controlled oxide" process.