# A Trench Isolation Process for BiCMOS Circuits

Stephen Poon and Craig Lage

Advanced Products Research and Development Laboratory, Motorola Inc., 3501 Ed Bluestein Blvd., Austin, Texas 78721

### ABSTRACT

A new isolation process using 1  $\mu$ m deep trench is developed for BiCMOS circuits. Well behaved MOSFETs and NPN devices with excellent parasitic performance were achieved. Low leakage diodes with butted junctions were demonstrated by inclusion of an oxidation barrier in the trench liner and utilizing a GeO2 doped oxide with matched thermal coefficient of expansion to the silicon substrate for trench fill. Planarity for arbitrary width isolation was obtained by using oxide RIE followed by chemical-mechanical polishing.

## INTRODUCTION

Trench isolation has been reported since the early 1980's as a replacement for LOCOS isolation for VLSI. However, process complexity associated with trench technology has restricted its appeal to a limited number of circuit applications while continuous modifications and improvements to LOCOS has enabled its implementation in a proposed 16 Mbit fast SRAM cell with 1  $\mu$ m active pitch [1]. Nevertheless, LOCOS is not expected to scale significantly beyond 1  $\mu$ m pitch due to its intrinsic limitations such as field oxide thinning, bird's beak encroachment, lack of planarity, and punchthrough. As a result, trench isolation is required to meet the demands of ULSI. However, a relatively simple process with sufficient benefits must be developed to gain wide acceptance.

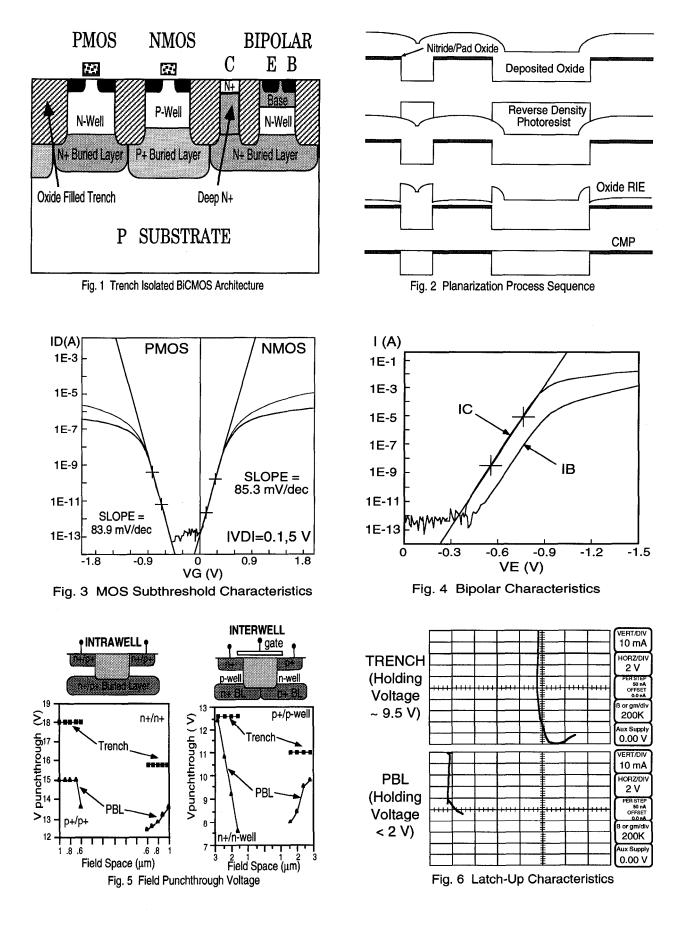

In this paper, a single isolation process utilizing a 1 µm deep trench with arbitrary width is proposed for BiCMOS circuits to avoid the complexity of shallow and deep trench isolation typically employed in high performance BiCMOS technology [2]. A schematic representation of the structure is shown in Figure 1. Latchup immunity, intrawell and interwell isolations, reduced parameter capacitance, as well as bipolar parasitic reduction are simultaneously satisfied with the proposed structure. The processing technique used to fabricate this structure and the electrical results achieved are described.

## FABRICATION

The process platform was adopted from a 0.5  $\mu$ m BiCMOS technology developed for 4 Mbit fast SRAMs [3]. Epi thickness is optimized to ensure up-diffusion from the buried layers to merge with the trench bottom to obtain the desired isolation and parasitic characteristics. A hard mask is used to protect the active regions for etching of a 1  $\mu$ m depth trench into the substrate. Both thermal oxide and composite thermal oxide/deposited nitride trench liners were evaluated along with several chemical vapor deposited oxides to determine the most suitable combination of

processes to minimize defect generation in the substrate and to minimize seam or void formation in narrow width trenches.

A combination of oxide RIE and chemical mechanical polishing process [4,5] is used for the planarization of arbitrary width trench. A schematic cross section of the planarization process sequence is shown in Figure 2. Compared to [4], this planarization sequence has a reduced number of process steps and has replaced the more complex planarization etchback process with an oxide RIE process. At this point, MOS and bipolar devices were fabricated using previously reported processes [3] to evaluate the merit of the proposed structure.

## RESULTS AND DISCUSSION

Transistor characteristics were measured on both CMOS and non-self-aligned NPN devices. Typical 0.5 µm Wdrawn subthreshold characteristics are shown in Figure 3. Both n- and p- channel devices exhibit ideal behavior with no degradation of the subthreshold slope. A Gummel plot for 0.8 µm emitter NPN is shown in Figure 4. Functional BiCMOS and ECL ring oscillators were also achieved.

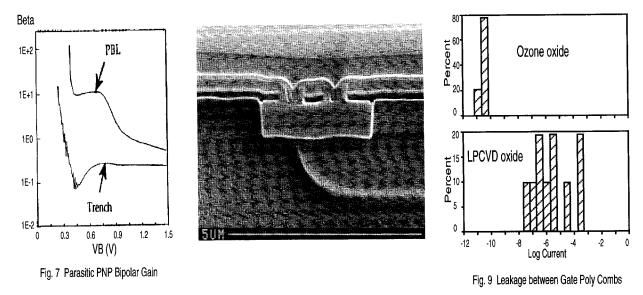

Field punchthrough voltage on intrawell and interwell isolation structures are shown in Figure 5. Results measured on trench isolated structures were independent of field width and are well above 10 volts. Holding voltage for latchup and parasitic bipolar gain are improved compared to a PBL isolation control because current path in the substrate is interrupted by the trench bottom reaching into up-diffusion from the buried layer. These results are shown in Figures 6 and 7, respectively. A SEM micrograph which illustrates this is shown in Figure 8.

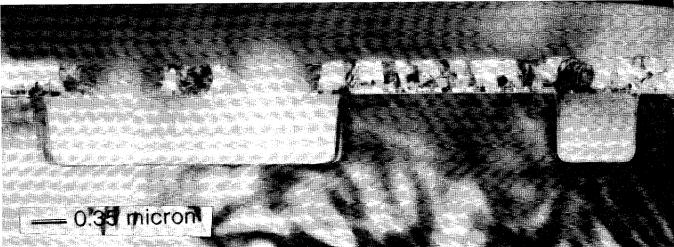

Deposited oxides are typically known to create voids and weak seams in narrow width and high aspect ratio trenches after wet strips/cleans due to poor step coverage. However, this problem is improved with ozone enhanced depositions [6,7] and ECR deposited films. Leakage current measured between gate poly combs in an on-pitch array for two different oxide trench fill is shown in Figure 9. A TEM cross section micrograph showing planar and defect-free isolation trench is shown in Figure 10.

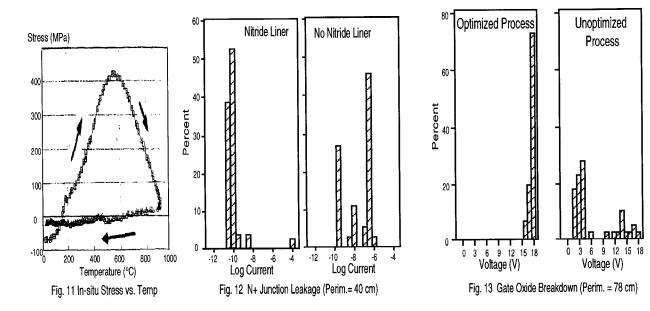

In order to alleviate stress induced leakage caused by substrate defects due to oxidation and other thermal processes in 1  $\mu$ m deep oxide filled trench, composite thermal oxide/CVD nitride trench liner [8,9] and trench fill with matched thermal coefficient expansion to the substrate [6] were evaluated. Stress measurement obtained on oxide trench fill film doped with GeO<sub>2</sub> is shown in Figure 11. Leakage measured on butted diodes with and without nitride liner are compared in Figure 12.

Gate oxide thinning at the trench corner which can degrade intrinsic dielectric breakdown was avoided by careful optimization of the process module. The results are shown in Figure 14.

#### SUMMARY

A simple trench isolation process that can simultaneously satisfy several requirements for submicron BiCMOS circuits is proposed and described. Well-behaved devices with excellent isolation and parasitic characteristics are demonstrated.

#### ACKNOWLEDGEMENTS

The authors wish to thank Phil Tobin, Asanga Perera, Fred Walczyk, David Burnett, Hsing Tseng, Jeff Lutze, and Jerry Sebek for technical discussions and measurements. Process support from Jung-Hui Lin, Kent Cooper, and the pilot line personnel of APRDL. Vendor support from Mel Hoffman of Westech, Jeff Bell of QTI, Todd Curtis of Watkins-Johnson, and the ECR process engineering team of Lam Research are sincerely appreciated. Rick Sivan and Lou Parrillo are acknowledged for their managerial support.

#### REFERENCES

- [1] J.D. Hayden, M.P. Woo, R.C. Taft, P. Pelley, B.-Y. Nguyen, C. Mazure, P.U. Kenkare, K. Kemp, R. Subrahmanyan, A.R. Sitaram, J-H. Lin, J. Ko, C. King, C. Gunderson, and H.C. Kirsch, 'A High-Performance Quadruple Well, Quadruple Poly BiCMOS Process for Fast 16Mb SRAMs', IEDM Technical Digest, pp. 819 - 822, 1992.

- [2] G.G. Shahidi, J. Warnock, B. Davari, B. Wu, Y. Taur, C. Wong, C.L. Chen, M. Rodriguez, D.D. Tang, K. Jenkins, P.A. McFarland, R. Schulz, D. Zicherman, P. Coane, D. Klaus, J.Y.C. Sun, M. Polcari, and T.H. Ning, 'A High Performance BiCMOS Technology Using 0.25 μm CMOS and Double Poly 47 GHz Bipolar', VLSI Tech. Symp. Digest, pp. 28 - 29, 1992.

- [3] T.C. Mele, J. Hayden, F. Walczyk, M. Lien, Y.C. See, D. Denning, S. Cosentino, and A.H. Perera, 'A High Performance 0.5 μm BiCMOS Triple Polysilicon Technology for 4Mb Fast SRAMs', IEDM Technical Digest, pp. 481 - 484, 1990.

- [4] B. Davari, C.W. Koburger, R. Schulz, J.D. Warnock, T. Furukawa, M. Jost, Y. Taur, W.G. Schwittek, J.K. DeBrosse, M.L. Kerbaugh, and J.L. Mauer, 'A New Planarization Technique, Using a Combination of RIE and Chemical Mechanical Polish (CMP)' IEDM Technical Digest, pp. 61 - 64, 1989.

- [5] S. Poon, A. Gelatos, A.H. Perera, and M. Hoffman, 'A Manufacturable Chemical-Mechanical Polish Technology with a Novel Low-Permittivity Stop-Layer for Oxide Polishing', VLSI Tech. Symp. Digest, pp. 115 - 116, 1993.

- [6] J. Bell, S. Fisher, K. Maeda, and S. Poon, 'Characterization of Germanium Doping in TEOS/Ozone Films for Trench Fill Applications', Schumacher Dielectrics and CVD Metallization Symp. Proceedings, February,1993.

- [7] J.P. West, H.W. Fry, and S. Poon, 'The Application of APCVD/Ozone Thin Films in ≤ 0.5 μm IC Fabrication: Trench and Inter-metal Isolation and Gap Fill', SPIE International Symposium on Microelectronic Processing, September, 1993.

- [8] C.W. Teng, C. Slawinski, and W.R. Hunter, 'Defect Generation in Trench Isolation', IEDM Technical Digest, pp. 586 - 589, 1984.

- [9] S.R. Stiffler, J.B. Lasky, C.W. Koburger, and W.S. Berry, 'Oxidation-Induced Defect Generation in Advanced DRAM Structures', IEEE Trans. Electron Devices, vol. 37, no. 5, pp. 1253 - 1258, 1990.

Fig. 10 TEM micrograph showing planar and defect free trench