# A High Density 0.10µm CMOS Technology Using Low K Dielectric and Copper Interconnect

S. Parihar, M. Angyal\*, B. Boeck, D.Reber, A.Singhal, T.Van Gompel, R. Li, B. Wilson, M. Wright, J. Chen, P. Grudowski, Y. Jeon, W.Qi, X. Bai, L. Parker, K. Strozewski, D. Smith, S. Roling, T. Sparks, T. Stephens, F. Huang, R. Mora, M. Aminpur, K. Hellig, L. Vishnubhotla, Y. Solomentsev, V. Arunachalam, A. Phillips, K. Junker, S. Filipiak, N. Ramani, M. Turner, M. Rendon, J. Molloy, K. McGuffin, A. Michel, R. Pena, D. Rose, J. Schmidt, M. Smith, M. Wilson, L. Terpolilli, P. Le, J. Sun<sup>†</sup>, R. Ross, K.Yu, M. Hall, P. Ingersoll, M. Woo, G. Yeap and C. Lage

Motorola DigitalDNA Laboratories and AMD Technology Development Group 3501 Ed Bluestein Blvd, MD: K-10, Austin, TX 78721. email:ra4009@email.sps.mot.com, (512) 933-3792 \* Present Address: IBM, Hopewell Junction, NY 12533 <sup>†</sup> Present Address: Silicon Laboratories, Austin, TX 78735

# ABSTRACT

In this work components of the next generation 0.10  $\mu$ m CMOS technology are presented. They form the core of a platform encompassing logic, non volatile memory, and analog blocks. High performance bulk devices use 18 Å gate oxide (24 Å inversion Tox) while low power devices use 25 Å gate oxide (31 Å inversion Tox) for reduced gate leakage. Gate lengths range from 65 nm for the high performance devices to 90nm for the low power devices. Both 3.3V and 2.5V I/Os are supported using 70 Å and 50 Å oxide devices. The backend employs low-k (k ~ 3) dielectric with multiple levels of Cu metallization. The high density 6T SRAM cell size is 1.33  $\mu$ m<sup>2</sup>.

| Table 1  | τ. | avout | Rules | for | 0.10 | um   | CMOS  | Technology |

|----------|----|-------|-------|-----|------|------|-------|------------|

| 1 auto 1 | ີ  | ayour | ruics | 101 | 0.10 | μiii | CINOS | recimology |

| Layer                 | 0.13 <i>µ</i> m | 0.10 µm   | Shrink |

|-----------------------|-----------------|-----------|--------|

| Active Line/Space     | 0.18/0.18       | 0.11/0.14 | 31%    |

| Poly Line/Space       | 0.15/0.21       | 0.10/0.14 | 33%    |

| Contact Size/Space    | 0.18/0.18       | 0.12/0.14 | 28%    |

| Contact Space to Poly | 0.105           | 0.08      | 24%    |

| Metal 1 Line/Space    | 0.18/0.18       | 0.12/0.12 | 33%    |

| Metal 2-8 Line/Space  | 0.21/0.21       | 0.14/0.14 | 33%    |

| Via Size/Space        | 0.21/0.21       | 0.13/0.15 | 33%    |

Fig. 1 Top view SEMs of SRAM isolation pattern for (a) no corrections applied, (b) corrections applied.

# **PROCESS INTEGRATION**

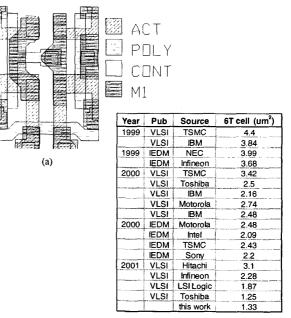

Key design rules are shown in Table 1 along with a comparison to the previous 0.13  $\mu$ m process node [1]. Overall, about a 30% shrink is achieved. These rules enable a 6T SRAM cell with area of 1.33  $\mu$ m<sup>2</sup> to be realized. Fig. 2 (a) shows the cell layout through metal 1 while Fig. 2 (b) is a list of other recently published 6T cells. In order to realize these rules, 193 nm photolithography is employed along with extensive optical proximity correction (OPC) at all critical levels. As an example of this, Fig. 1 shows the SRAM bitcell isolation pattern with and without corrections applied.

(b)

Fig. 2 (a) 1.33 µm<sup>2</sup> bitcell layout (b) recent reported SRAM cell sizes

Fig. 3 SEMs showing void free oxide fill of subnominal and nominal isolation trenches.

Table 2 0.10µm Process Features

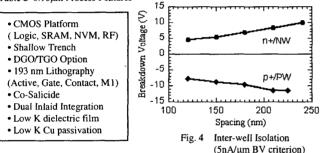

Key process features are listed in Table 2. In order to accommodate wireless RF applications, p- substrates are supported in addition to p- epi on p+ substrates to reduce the inductor losses. The integration starts with shallow trench isolation and a 3.5 KÅ trench depth. A high density plasma oxide fill process is used which is capable of void free fill down to below 0.12  $\mu$ m wide trenches (see Fig. 3). The interwell electrical isolation is shown in Fig. 4 which illustrates low leakage down to 0.12  $\mu$ m diffusion to well space.

Fig. 6 1.33  $\mu$ m<sup>2</sup> SRAM cell post gate etch

Fig. 5 (a) NVM bitcell (b) tunnel oxide IV

In keeping with system-on-chip (SoC) technology requirements, the 0.10  $\mu$ m technology supports an embedded NVM module. NVM cell sizes below 0.20  $\mu$ m<sup>2</sup> are achievable without adding excessively complex processing; Figure 5 (a) shows a 0.19  $\mu$ m<sup>2</sup> cell, and cells as small as 0.16  $\mu$ m<sup>2</sup> are in development. Processes for isolation, gate, and metallization are developed to be NVM compatible from the beginning. For example, particular attention is paid to trench corner rounding to suppress edge tunneling currents. Fig 5(b) shows the tunnel oxide IV characteristics that exhibit no edge enhancement as desirable for reliable floating gate cell operation.

After the wells are implanted, I/O gate oxide is grown and patterned followed by an optional intermediate gate oxide and then the core gate oxide. Polysilicon gate layer is deposited and patterned with 193nm lithography. An inline SEM picture of the SRAM bitcell is shown in Fig. 6 post gate etch. Shallow extensions and conventional nitride spacers are used to control the extent of the source/drain implants. Cobalt silicide on active and poly regions is employed to reduce contact resistance and tungsten plugs connect up to a single inlaid Cu metal 1. Fig. 7 shows a cross section of the SRAM bitcell through the bitline contacts.

Fig. 7 SRAM cell post M2 Cu polish

Fig. 8 Deprocessed bitcell view showing W plugs and poly with spacers

A top down SEM of the deprocessed bitcell is shown in Fig. 8. After metal 1, a dual inlaid copper integration is used to process the subsequent metal and via levels. To reduce the backend wire capacitance, a low-k dielectric film is used for both the dielectric and barrier layer.

# **DEVICE PERFORMANCE**

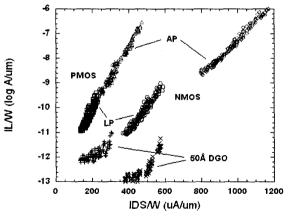

This technology supports two core device types: a 25 Å gate oxide low leakage device (LP) for low power applications and an 18 Å high performance device (AP). Both devices make extensive use of halo implant and S/D engineering to meet the performance targets which are summarized in Table 3. Ion/Ioff for NMOS and PMOS devices are shown in Fig. 9. The LP NMOS and PMOS transistors meet 420/170  $\mu$ A/um at 20 pA/µm leakage while the AP devices reach 920/400  $\mu$ A/um at 20 nA/µm leakage. Data for the I/O devices is also shown in Fig. 9. Aggressive I/O performance is achievable while meeting intrinsic HCI reliability goals.

Fig. 9 Ion/loff curves for core and I/O devices

| Table 3 | Transistor | Targets |

|---------|------------|---------|

|---------|------------|---------|

| Transistor                    | HIP8LP | HIP8AP    |                             |                                                                                                                |

|-------------------------------|--------|-----------|-----------------------------|----------------------------------------------------------------------------------------------------------------|

| Туре                          | Target | Target    | 2.5V I/O                    | 3.3V I/O                                                                                                       |

| V <sub>DD</sub> (V)           | 1.2    | 1.2 (1.0) | 2.5                         | 3.3                                                                                                            |

| T <sub>ox, optical</sub> (nm) | 2.5    | 1.8       | 5                           | 7                                                                                                              |

| L <sub>poly</sub> (nm)        | 90     | 65        | 280                         | 375                                                                                                            |

| NMOS                          |        |           |                             |                                                                                                                |

| T <sub>ox, inv</sub> (nm)     | 3.1    | 2.4       | 5.5                         | 7.3                                                                                                            |

| l <sub>on</sub> (μΑ/μm)       | 420    | 910(680)  | 575                         | 570                                                                                                            |

| l <sub>off</sub> (nA/μm)      | 0.02   | 20 (10)   | 0.003                       | 0.002                                                                                                          |

| l <sub>g</sub> (nA/μm)        | 0.002  | 3         |                             | and a second |

| PMOS                          |        |           |                             |                                                                                                                |

| T <sub>ox, inv</sub> (nm)     | 3.2    | 2.5       | 5.6                         | 7.4                                                                                                            |

| l <sub>on</sub> (μΑ/μm)       | 180    | 400(290)  | 250                         | 250                                                                                                            |

| l <sub>off</sub> (nA/μm)      | 0.02   | 20 (10)   | 0.003                       | 0.003                                                                                                          |

| l <sub>g</sub> (nA/μm)        | 0.0002 | 1         | and an an an an an an an an | a a a a a a a a a a a a a a a a a a a                                                                          |

To support SoC design methodology, a greater variety of device options is required. Controlling device leakage becomes a key goal of process technology when low voltage performance requirements dictate ever thinner gate oxides. In order for core circuit blocks to be utilized for both low power portable applications and high performance applications without extensive redesign, several process options must be available. These options include multiple gate oxide thicknesses on the same die [2,3], isolated well biasing schemes, and high Vt transistors. All three options are supported in our 0.10  $\mu$ m process flow.

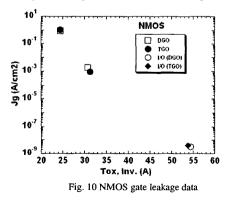

As an example we consider the triple gate oxide option. With gate oxides scaling in thickness below 20 Å, it becomes important to limit the gate tunneling current in certain blocks such as memories in order to meet standby current constraints. Therefore we offer the use of triple gate oxide (TGO) with the high performance device flow. Fig. 10 compares electrical Tox and gate leakage results for 50 Å I/O flows with (TGO) and without (DGO) the intermediate gate oxide. It is apparent that the intermediate gate oxide can be inserted with little impact to either the core gate oxide or I/O oxide thickness, and provides a reduction in gate leakage of three orders of magnitude.

Fig. 11 (a) Metal trench etch (b) via etch

# BACKEND

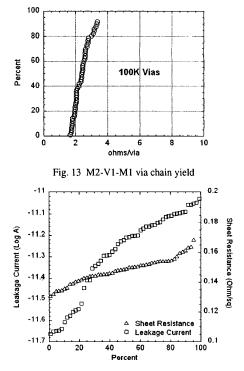

Both the new 193 nm resists and the use of low-k materials as interlevel dielectrics (ILD) pose significant challenges to the backend integration for 0.10  $\mu m$  technologies. We are addressing these challenges through the utilization of a novel patterning strategy. This patterning strategy provides improved process capability and margin for the aggressive geometries and pitches specified for this technology node. Fig. 11 demonstrates this patterning capability for 0.30 µm pitch inlaid metal trenches and 0.12 µm sized inlaid vias etched into the low-k (k ~ 3) ILD. The minimum metal width is approximately 0.12  $\mu$ m while the 0.10  $\mu$ m diameter at the bottom of the via corresponds to an aspect ratio of ~ 6:1. With this integration we have produced vielding via chains with resistances in the range of 2 to 4 ohms/via as shown in Fig. 13. Excellent barrier step coverage and voidfree copper fill of these structures is indicated from SEM cross-sections in Fig. 12 for vias with bottom diameters as small as 0.12 um. The capability of the inlaid metal patterning and copper polish processes to maintain good electrical isolation at these geometries is evident in the lineto-line leakage data presented in Fig. 14 for 0.30 µm pitch features. The uniformity of the patterning and polish processes is also apparent from the sheet resistance data shown in Fig. 14 for 0.12 µm wide metal features.

#### CONCLUSIONS

A dense 0.10  $\mu$ m technology has been developed incorporating dual inlaid Cu and low-k dielectric in the backend and 193 nm lithography at all critical levels. Two core devices along with a triple gate oxide option provide flexibility in meeting design constraints for power, performance, and leakage. Low-k interlevel dielectric and passivation layers help reduce the backend capacitance at the tight metal pitches of this technology node. Fig. 12 Dual inlaid SEM. Final via size = 0.12 um

# ACKNOWLEDGEMENTS

The authors thank and acknowledge the collaboration of our colleagues in process technology development in the Dan Noble Center. Management support from Bob Yeargain, Nick Kepler and Greg Bartlett is greatly appreciated.

### REFERENCES

[1] A. Perera et. al., IEDM December 2000.

[2] K. Miyashita et. al., VLSI Symposium, June 2001.

[3] A. Ono et. al., VLSI Symposium, June 2001.

Fig. 14 Metal 1 snake/comb data for 0.30 µm pitch