# Submicron BiCMOS Technologies for Super Computer and High Speed System Implementation

B. Bastani, M. Biswal, A. Iranmanesh, C. Lage, L. Bouknight V. Ilderem, A. Solheim, W. Burger, R. Lahri, J. Small

> National Semiconductor 1111 39th Avenue S.E. Puyallup, WA 98374

### ABSTRACT

This paper describes submicron process technologies that allow a full implementation of CPU, first level Cache, second level Cache, and the main memory in a BiCMOS approach. CPU Standard Cells up to 100K ECL gate density with embedded CMOS and BiCMOS SRAM, X9 Cache memories, and 1 Meg ECL I/O SRAMs with less than 7ns access time are achieved.

# INTRODUCTION

State-of-the-art BiCMOS technologies are vital tools of today's manufacturing and as such they are being extensively used to realize high performance semiconductor products while maintaining high density at moderate power consumption. Due to extra processing steps, cost per wafer for BiCMOS processes is higher than pure CMOS or Bipolar technologies. However, due to performance and density improvement BiCMOS processes enjoy lower cost per gate than ECL at a lower power level, comparable to CMOS products. For memory products BICMOS processes offer higher speed performance along with TTL and ECL I/O options. Using BiCMOS processes tailored for ASIC applications, on the other hand, memory arrays can be incorporated into existing or new designs adding to product versatility and leading to increased performance for systems employing such products.

In this paper two major BiCMOS technology families are discussed and compared in terms of processing and device performance. In addition areas of application for each one of these processes as related to the total system solution will be explored.

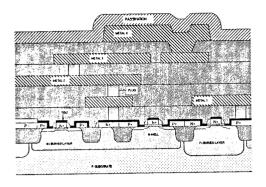

#### ASIC & MEMORY BICMOS FAMILIES

Currently two major high performance BiCMOS technology families exist in National Semiconductors. A technology road map for these process families is shown in TABLE-I. Advanced BiCMOS process family, known as ABiC, is the family of BiCMOS technologies developed for high performance ASIC applications with emphasis on embedded CMOS, BiCMOS or ECL memory as well as BiCMOS and ECL gate array and standard cells. In development of ABiC process, National Semiconductor's state-of-the-art ASPECT process [1,2], has been successfully combined with high performance CMOS process [3,4,5]. The second technology family, known as BiCMOS, is mainly developed for SRAM applications where dense 4T MOS memory cells combined with high speed bipolar logic leads to very high levels of device integration. Final bipolar and CMOS device cross sections for current generation of the ABiC family, ABiC IV, are shown in Fig.1. In Fig.2 process cross section for the 0.8 µm BiCMOS IV technology [6,7] is shown. Despite differences in architecture a high degree of similarity and synergy exists between these processes. Device isolation in both processes is accomplished using an advanced, low encroachment fully recessed oxide isolation process optimized for small bird's beak and planarity as well as defect density. The N+ and P+ twin buried layers form retrograde well profiles for CMOS transistors and result in soft error and latch up immunity. The gate oxide is 150 A thick and in the ABIC IV process is protected by a thin layer of polysilicon during subsequent mask/etch process. The major difference between technologies is in the use of the polysilicon layers.As shown in Fig.1, in the ABIC IV a single layer of polysilicon is used for simultaneous formation of gate, emitter, source/drain and base contacts as well as several high precision poly resistors. The same layer of polysilicon is silicided and used for local interconnection, increasing design flexibility and packing density.

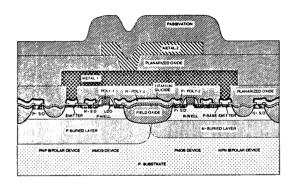

The BiCMOS IV process on the other hand is a double poly technology where the first poly layer forms the gate of the CMOS devices. The second poly layer forms emitter of bipolar transistors as well as high value load resistors for high density 4T cell memory implementation. The area of memory cell in BiCMOS IV is about 37  $\mu$ m2. The second layer of poly is also selectively silicided, facilitating the formation of low-resistance local interconnects leading to smaller memory foot print and pitch. In contrast, 6T memory cells are more appropriate in ABiC IV where a larger memory cell area of about 100  $\mu$ m2 can be tolerated. Other key features for these technologies are summarized in TABLE-II.

## **ELECTRICAL PERFORMANCE**

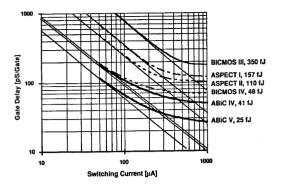

Key device electrical parameters are summarized in TABLE-III. Both technologies enjoy respectable Idsat of 0.4 mA/ $\mu$ m for NMOS and 0.2 mA/ $\mu$ m for PMOS devices and for nominal effective channel length of 0.6  $\mu$ m. Unity gain frequency, Ft, is about 15 GHz for bipolar transistors. ABiC IV devices , however, have lower extrinsic base resistance as well as S/D resistance due to self aligned silicide. Smaller bipolar foot print in ABiC IV leads to reduced device capacitance as shown in TABLE-III. Gate delay information for ABiC IV and BiCMOS IV are summarized in TABLE-IV. From TABLE-IV both technologies offer similar high performance for CMOS and BiCMOS gates. Delay x power products for several high performance technologies including ABiC IV and BiCMOS IV is given in Fig.3 .ECL performance in ABiC IV technology is superior due to highly optimized bipolar architecture and with gate delay of about 200 psec at 50  $\mu$ A of current, high levels of integration can be achieved.ABiC IV also offers optimal interconnection performance of less than 1 pS/mil (40 pS/mm) for 4 layers of interconnection.

CH2909-0/90/0000/0007\$01.00 © 1990 IEEE

## PRODUCT CAPABILITIES

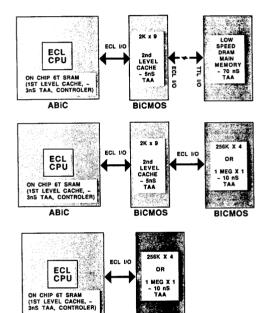

The BiCMOS process family is primarily designed with high speed and dense SRAM applications in mind. Several high performance memory products such as 256K SRAM [8], 3.5 ns 2Kx9 self timed SRAM [9], 6.8 ns 1MB SRAM with ECL and TTL I/O [10] have been designed in BiCMOS III and BiCMOS IV technologies. The ABiC process, on the other hand, due to smaller and higher performance bipolar devices, is attractive for bipolar intensive applications such as high performance 50 to 120K gates ECL logic array, 100 to 200K gates CMOS/BICMOS logic array and high density ASIC products requiring embedded memories. These two technologies provide a total high-performance system solution. For example Fig.4 illustrates three high speed systems of CPU Standard Cells up to 100K ECL gate density with embedded CMOS and BiCMOS SRAM, X9 Cache memories, and 1 Meg ECL I/O SRAMs with less than 7ns access time.

## CONCLUSION

State-of-the-art BiCMOS technologies have been developed leading to total system solutions for high performance applications.

### REFERENCES

- A. Iranmanesh *et al*, BCTM Technical Digest, pp 30-32, BCTM, 1989. [1].

- [2]. M. Vora et al, IEDM Technical Digest, pp 690-694, IEDM, 1984. [3].

- V. Ilderem et al, CICC 1990 Proceeding, pp 18.6.1-18.6.4

- [4].

- [5]. [6].

- A. Iranmanesh *et al*, VLSI 1990. A. Iranmanesh *et al*, BCTM 1990. W. Burger *et al*, IEDM Technical digest, pp 421, 424, IEDM, 1989.

- [7]. [8].

- W. Burger *et al*, BCTM 1990.

B. Bastani *et al*, Proc. Symp. VLSI Tech. pp 41 -42,

- VLSI 1987.

- [9]. [10]. D. Wendell et al, VLSI 1990.

- B. Kertis et al, VLSI 1990.

Fig.1 Process Cross section for ABiC IV technology.

Fig.3 ECL gate Speed x Power product plots for several high performance technologies including ABiC IV and BiCMOS IV.

Fig.2 Process Cross section for BiCMOS IV technology.

BICMOS

ABIC

Fig.4 Several high performance system realizations using advanced BiCMOS technologies.

| TABLE-I | Technology road map for memory and ASIC BiCMOS families. |

|---------|----------------------------------------------------------|

|---------|----------------------------------------------------------|

| GENERATION                                                                                                                                                                                                                                                                                    |                                  | ASIC<br>BICMOS   | LEADING<br>PRODUCT                                                                                                                                                                                                                           |                                                                              | DATE<br>INTR( | OF<br>DDUCTION                                                                                                         |          |                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| IV                                                                                                                                                                                                                                                                                            | 0.8                              | ABiC IV          | 100 K ECL/BiCMOS<br>156K CMOS SRAM                                                                                                                                                                                                           | Std Cell+                                                                    | 1990          |                                                                                                                        |          |                                                                                                                                         |

| v                                                                                                                                                                                                                                                                                             | 0.5                              | ABiC V           | 200 K ECL/BiCMOS<br>1Mb CMOS SRAM                                                                                                                                                                                                            | Std Cell+                                                                    | 1992          |                                                                                                                        |          |                                                                                                                                         |

| GENERATION                                                                                                                                                                                                                                                                                    |                                  | MEMORY<br>BICMOS | LEADING<br>PRODUCT                                                                                                                                                                                                                           | DATE OF<br>INTRODUC                                                          | CTION         |                                                                                                                        |          |                                                                                                                                         |

| III                                                                                                                                                                                                                                                                                           | 1.0                              | BiCMOS III       | 256 K SRAM                                                                                                                                                                                                                                   | 1988                                                                         |               |                                                                                                                        |          |                                                                                                                                         |

| IV                                                                                                                                                                                                                                                                                            | 0.8                              | BiCMOS IV        | 1 Mb SRAM                                                                                                                                                                                                                                    | 1990                                                                         |               |                                                                                                                        |          |                                                                                                                                         |

| V                                                                                                                                                                                                                                                                                             | 0.5                              | BiCMOS V         | 4 Mb SRAM                                                                                                                                                                                                                                    | 1992                                                                         |               |                                                                                                                        |          |                                                                                                                                         |

|                                                                                                                                                                                                                                                                                               |                                  | chnology feat    | tures. Areas of major<br>by *.                                                                                                                                                                                                               | TABLE                                                                        | <u>-III</u>   | Key electrical                                                                                                         | paramet  | ers.                                                                                                                                    |

|                                                                                                                                                                                                                                                                                               |                                  |                  | -                                                                                                                                                                                                                                            | PARAM                                                                        | IETER         | ABiC IV                                                                                                                |          | <b>BiCMOS IV</b>                                                                                                                        |

| ABiC IV                                                                                                                                                                                                                                                                                       |                                  |                  | <b>BICMOS IV</b>                                                                                                                                                                                                                             | NPN:<br>Emitter A                                                            |               | 0.8 x 1.6 μm2                                                                                                          | <b>、</b> | 0.8 x 1.5 μm2                                                                                                                           |

| *Single Poly<br>*6T memory cell<br>*(Area ~ 100 μm2)<br>Twin Buried Layer<br>Retrograde Well<br>PLDD, NLDD<br>150 A Gate Oxide<br>Local Interconnect<br>Tungsten Plugs<br>*4 Layer Metallizat<br>*2.5μm Metal 1,2,<br>High Performance<br>PNP<br>*Silicide 1st poly, S<br>*Integrated Well Ta | ion<br>3 Pitch<br>PNP<br>6/D & F | Base             | *Double Poly<br>*4T memory cell<br>*(Area ~ 37 µm2)<br>Twin Buried Layers<br>Retrograde Well<br>PLDD, NLDD<br>150 A Gate Oxide<br>Local Interconnect<br>Tungsten Plugs<br>*2 Layer Metallization<br>*1.8µm Metal 1 Pitch<br>High performance | Beta<br>BVebo<br>BVceo<br>Cjeb<br>Cjeb<br>Cjcs<br>Ft<br><i>CMOS:</i><br>Leff | лоs           | 0.6 V<br>15 V<br>8 V<br>3.3 fF<br>2.9 fF<br>10.2 fF<br>15 GHz<br>0.6 μm<br>0.75 V<br>-0.95 V<br>0.4 mA/μm<br>0.2 mA/μm |          | 0.5 μm<br>150<br>3.6 V<br>14 V<br>6 V<br>5.6 fF<br>5.2 fF<br>16.2 fF<br>15 GHz<br>0.6 μm<br>0.75 V<br>-0.95 V<br>0.4 mA/μm<br>0.2 mA/μm |

| TABLE-IV | Summary of ring oscillator gate delay values for BiCMOS IV and ABiC IV processes. |

|----------|-----------------------------------------------------------------------------------|

|          | processes.                                                                        |

| GATE TYPE                 | <u>DELAY [pS], CL=0</u><br>ABIC IV BICMOS IV |          | DELAY [pS], CL=1.0 pF<br>ABIC IV BICMOS IV |            |  |  |

|---------------------------|----------------------------------------------|----------|--------------------------------------------|------------|--|--|

| CMOS                      | 89                                           | 86       | 480                                        | 491        |  |  |

| BICMOS                    | 125                                          | 122      | 320                                        | 341        |  |  |

| ECL (1mA)<br>ECL (200 μA) | 48<br>72                                     | 65<br>85 | 138<br>232                                 | 157<br>250 |  |  |